英特尔在近期技术展示中公开其18A工艺制程的AI芯片,采用背面供电与垂直堆叠设计,旨在缓解高算力场景下的能耗与散热瓶颈。据官方消息,该芯片面向数据中心与边缘AI推理等对能效比要求较高的应用,通过在晶圆背面布置供电线路与多层堆叠结构,缩短电流路径并提升晶体管密度,已在内部测试中显现出降低功耗与提升性能的潜力。

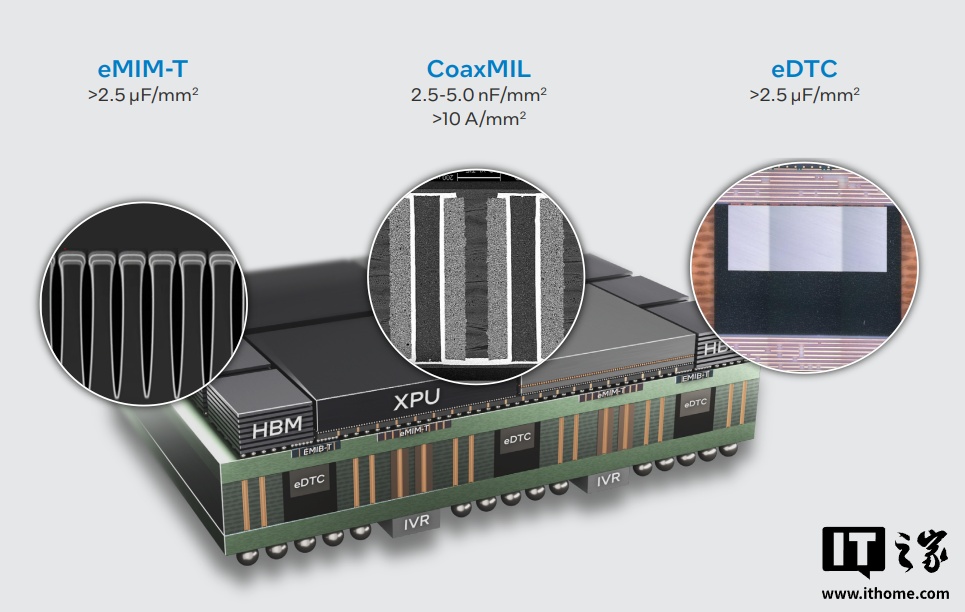

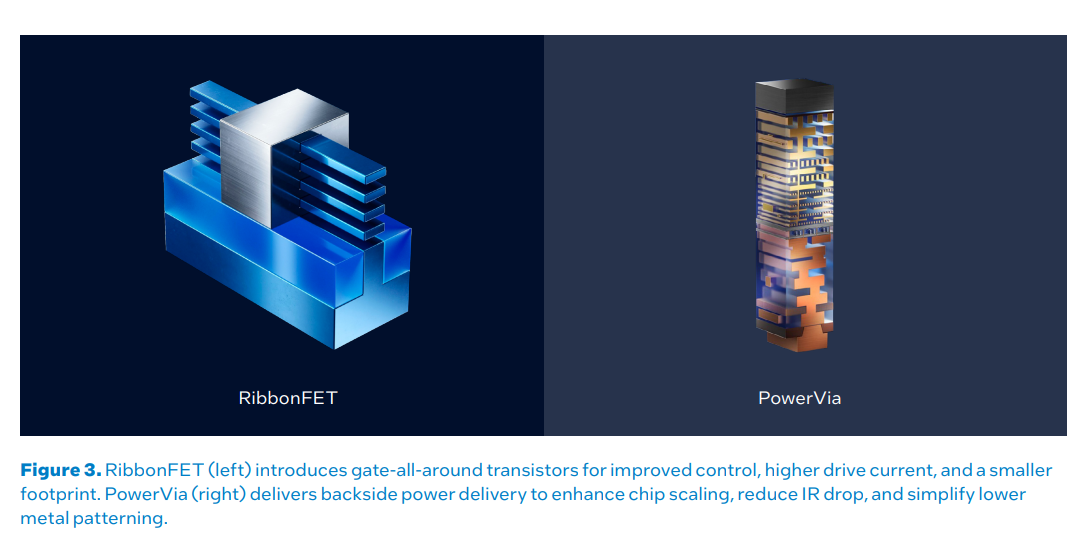

消息称,18A工艺在制程节点上引入背面供电(Backside Power Delivery)技术,将供电层由晶圆正面迁移至背面,可减少前端互连拥塞并降低电阻损耗,从而提升整体能效。垂直堆叠架构则允许逻辑单元与存储单元在三维空间中紧密排布,缩短数据搬运距离,提高片上通信效率。现场资料显示,该设计在运行大规模神经网络推理时,可在保持算力输出的同时降低单位计算能耗,对需要长时间满载运行的AI负载具有重要意义。芯片外围集成高速互连接口,便于与服务器主板及加速器模组协同部署,结构强度与散热方案亦针对密集堆叠进行优化。

在先进AI芯片设计中,功耗与散热已成为制约算力提升的关键瓶颈,英特尔此次展示的方案以制程与结构创新同步推进,为解决该问题提供了可验证路径。与仅依靠制程微缩或单纯增加芯片面积的既有做法相比,背面供电与垂直堆叠结合可在同等算力目标下减少发热量与供电压力,在数据中心部署中可降低冷却系统负荷并节约能源开销。该技术展示被视为业界探索高能效AI硬件的参考样本,也为后续量产方案在性能与可持续性之间取得平衡提供了实践依据。

此次技术展示凸显了英特尔在先进制程与AI芯片架构协同优化方面的进展。后续可关注该芯片的良率爬坡与规模化生产可行性,以及在真实AI负载下的能效验证结果。对于需在有限能耗预算内扩展AI算力的企业与研究机构,该方案的思路与设计方法具有实际参照价值。